SPECIFICATIONS

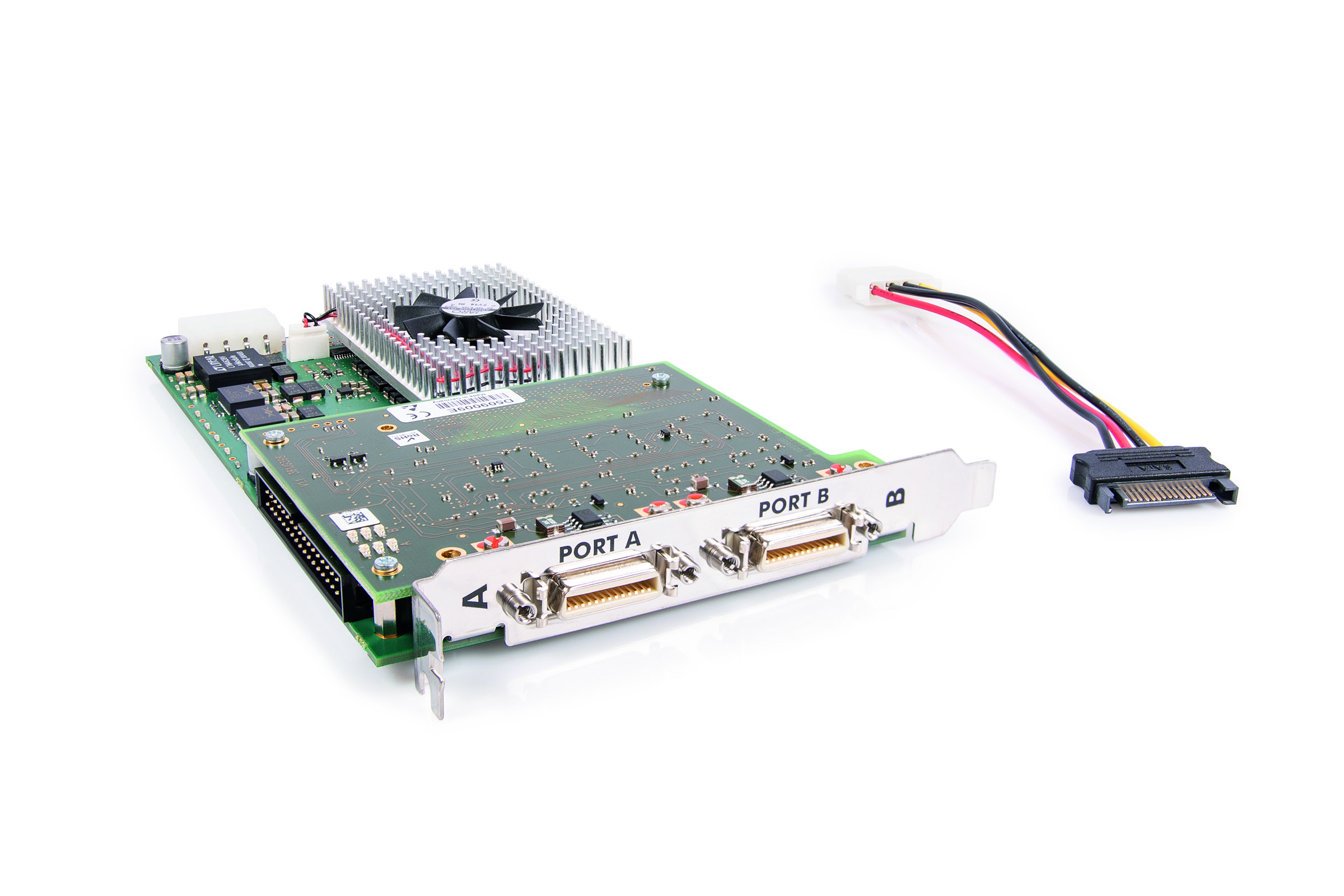

| Model | microEnable 5 ironman VD8-PoCL |

| Part Number | 108096 |

| Product Family | V-Line |

| Processor | Xilinx Virtex6 XC6VLX240T FPGA, Vision Processor |

| Onboard Memory | 1 GByte DDR3-RAM |

| Camera Interface | Cameralink 2.0 |

| Camera Connectors | 2 x MDR26 |

| Configurations | CL-FULL, Including Non-Standard Formats: Bilinear Color CL-deca (80-bit) |

| Power Output | PoCL SafePower: 4W @ 12V per Cable |

| Camera Format Support | Area Scan or Line Scan |

| Bit Depth | 8-16 bit Greyscale. 24-48 bit Color |

| Data Bandwidth | 850 MegaBytes/sec |

| Test Environment | Built-In Camera Simulator |

| PC Bus Interface | PCI Express x8 (Gen 2) DMA 3600 |

| PC Bus Interface Performance | up to 3600 MBytes/s (sustainable) |

| GPIO Synchronization and Control | Configurable Trigger System supporting several trigger modes (grabber controlled, external trigger, gated, software trigger) and shaft encoder functionality with backward compensation, Multi-Camera-Synchronization |

| GPIO Interface Summary | 8in/8out (max.), TTL or opto-coupled |

| Basic Processing Features | Tap Sorting (Sensor Readout Correction), Offset/Gain/Gamma correction, Invert, ROI, Image Selector, LUT |

MECHANICAL and ENVIRONMENTAL

| Dimensions | PCIe Standard Height Half-Length card: 167.64 mm (L) x 111.15 mm (H) |

| Power Consumption | 2.5 Amp @ 14 VDC |

| Operating Temperature | 0C – 50C (32F – 122F) |

| Storage Temperature | -50C to 80C (-58F to 176F) |

| Environmental Compliance | WEEE, RoHS, REACH |

SOFTWARE SUPPORT

| Software Drivers | Windows 10 / 8 / 7 (32-Bit), Windows 10 / 8 / 7 (64-Bit), Linux 32-Bit, Linux 64-Bit |

| Software Tools | microDisplay (Acquisition control and viewer), GenICam Explorer (Camera configuration tool), Documentation, microDiagnostics (Service tool), SDK, Device Drivers |

| Software API | Silicon Software SDK, .net interface |

| FPGA Programming | not programmable |

| BV-Software Compatibility | Common Vision Blox, Halcon |